36<sup>th</sup> Cycle

# Limit-Cycle Free Digitally Controlled Power **Converters and Innovative Design of a Capacitive Wireless Power Transfer Circuit** Ahmed Abdullah

Supervisor: Prof. Francesco Musolino, Prof. Paolo Crovetti

# **Research context and motivation**

voltage

$f_{\rm clk} = 5 \,\rm MHz$

$f_{\rm sw} = 100 \, \rm kHz$

$N_{\rm ADC} \ge 8 \text{ bits DC}$

$f_{\rm sw} \approx 10 \; {\rm MHz} \; {\rm range} \; requires$

$\succ$  Or, conversely

accuracy

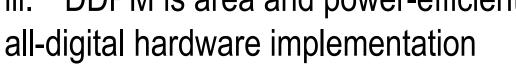

- Limit-cycle Free, Digitally Controlled Boost Converter based on DDPWM \*\*

- Digital controllers are more prevailing in switching-mode power converters

- flexibility, reliability, good performance, low cost and reduced susceptibility to aging.

- Boost converter used in photovoltaic systems, in battery powered and portable device applications Spectral characteristics of DDPM

- baseband digital-to-analog (D/A) conversion

- digital-based operational transconductance amplifiers

- analog-to-digital (A/D) conversion

- digitally-controlled power converters

- iii. DDPM is area and power-efficient

*limit to*

$N_{\rm ADC} \leq 5$  bits

NOT ACCEPTABLE

DC accuracy for most cases

$f_{\rm clk} > 2 \, \rm GHz$

**IMPRACTICALLY**

high clock frequency

# Adopted methodologies & Results

- Limit-cycle Free, Digitally Controlled Boost Converter based on DDPWM \*\*

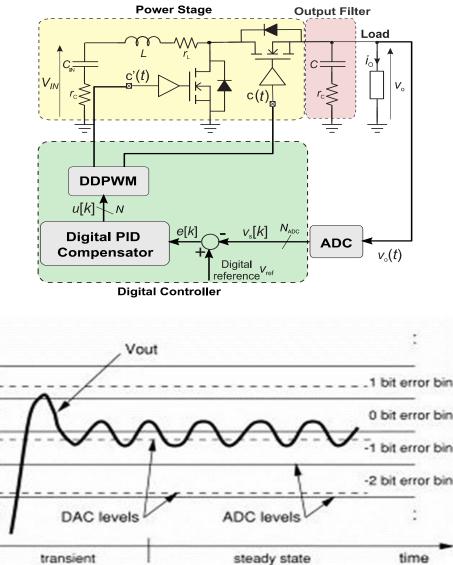

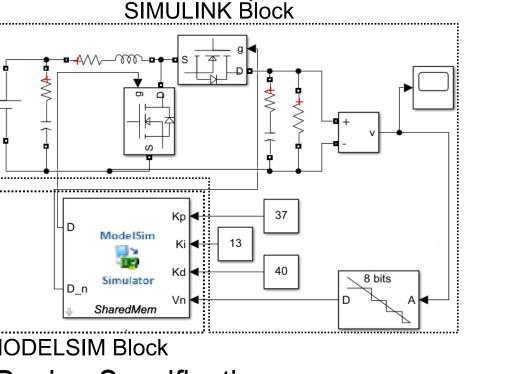

- **Co-simulation setup** SIMULINK Block

- Experimental Test Setup

- C2000 microcontroller board with onboard ADC and PWM modules

- Algorithm is programmed in C-language

- PCB designed boost converter

- EPC9006C board

- Limit-cycle Oscillations (LCOs)

- To remove LCOs,  $N_{DDPM} > N_{ADC}$

- Requires high clock frequency a)

- Limited DC accuracy. b)

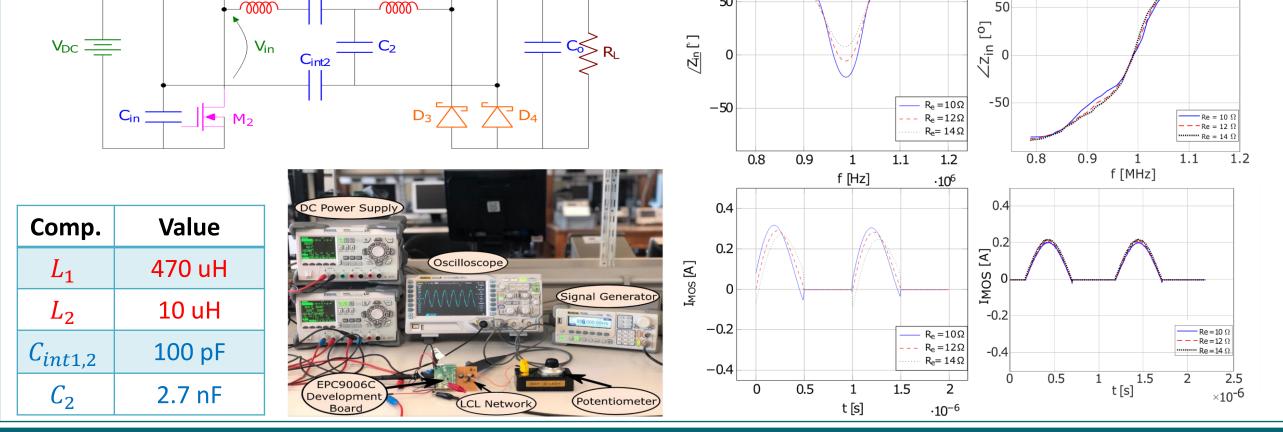

- Design and efficiency analysis of an LCL capacitive power transfer system with ••• **load-independent ZPA**

➢ Given

Capacitive based wireless Power Transfer CPT

[1] M. Usmonov, P. S. Crovetti, F. Gregoretti and F. Musolino, "Suppression of Quantization-Induced Limit Cycles in Digitally Controlled DC-DC Converters by Dyadic Digital Pulse Width Modulation," 2019 IEEE Energy Conversion Congress and Exposition (ECCE), 2019, pp. 2224-2231, doi: 10.1109/ECCE.2019.8913214.

[2] P. S. Crovetti, M. Usmonov, F. Musolino and F. Gregoretti, "Limit-Cycle-Free Digitally Controlled DC-DC Converters Based on Dyadic Digital PWM," in IEEE Transactions on Power Electronics, vol. 35, no. 10, pp. 11155-11166, Oct. 2020, doi: 10.1109/TPEL.2020.2978696.

# Addressed research questions/problems

- Limit-cycle Free, Digitally Controlled Boost Converter based on DDPWM \*\*

- Sigma-Delta ( $\Sigma$ - $\Delta$ ) modulation, multiphase PWM, digital thermometric dithering (DTD)

- Dyadic digital PWM (DDPWM)

- DDPWM is implemented on FPGA a)

- effective for LCO-free operation in a buck converter

- Buck converter  $V_o = V_{in}$ . D, while boost converter  $V_o = V_{in}/(1-D)$

- So, finer quantization steps at lower duty-cycle and coarser steps as duty-cycle increases.

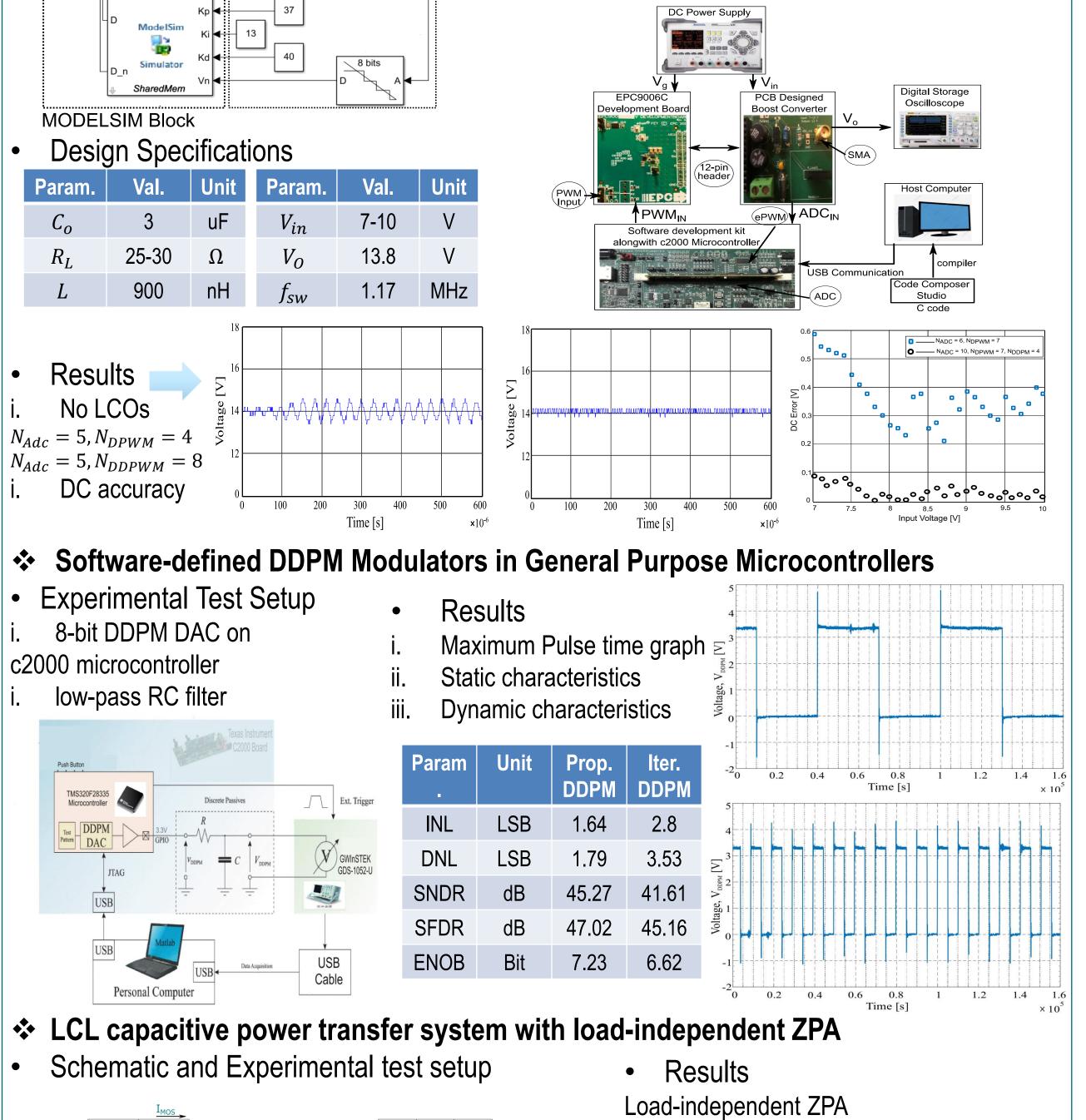

- Software-defined DDPM Modulators in General Purpose Microcontrollers \*

- Significant attention to digital HW implementation

- SW implementation in a microcontroller HW has not been specifically addressed

- ✤ LCL capacitive power transfer system with load-independent ZPA

- desirable feature in battery charger is the zero-phase angle (ZPA)

- ZPA operation must be load independent

### **Novel contributions**

- Limit-cycle Free, Digitally Controlled Boost Converter based on DDPWM ••• Dyadic Digital Pulse Width Modulation

- New and deterministic approach

- Effectively increase the DPWM resolution

- Spurious spectra pushed at high frequency

- **Software-defined DDPM Modulators** in General Purpose Microcontrollers

- New DDPM modulator architecture

- amenable to SW implementation on microcontroller.

- Compared to SW architecture resulting from straightforward translation of HW implementation.

# Submitted and published works

- A. Abdullah, F. Musolino and P. Crovetti, "Software-Defined DDPM Modulators for D/A Conversion by General-Purpose Microcontrollers," in IEEE Access, vol. 10, 2022, pp. 17515-17525

- P. Crovetti, R. Rubino, A. Abdullah and F. Musolino, "Emerging Relaxation and DDPM D/A Converters: Overview and Perspectives," 2022 IEEE 65th International Midwest Symposium on Circuits and Systems (MWSCAS), 2022, pp. 1-6

- Francesco Musolino, Ahmed Abdullah, Mario Pavone, Fabio Ferreyra, Paolo Crovetti, "Design and efficiency analysis of an LCL Capacitive Power Transfer system with Load-Independent ZPA," EPE'22 ECCE Europe, 2022

- A. Abdullah, F. Musolino and P. Crovetti, "Limit-Cycle Free, Digitally-Controlled Boost Converter based on DDPWM," in IEEE Access (to be submitted)

# **Future work**

- Limit-cycle Free, Digitally Controlled Boost Converter based on DDPWM \*\*

- In preparation to be submitted to IEEE Access

- Expand the research in the digitally controlled converter to limit the onset of LCOs

- Thesis writing and attend courses

- Collaborate with Prof. Francesco Musolino in conducting Power Electronics Lab

# List of attended classes

- 01DNZRV Emerging Ultra-low Voltage, Ultra-low Power Analog and Mixed-Signal Integrated Circuits for the IoT (06-22, 4)

- 01RGBRV Optimization methods for engineering problems (07-06-22, 6)

- 01DMQRV Power electronics for grid applications (06-22, 4)

- 08IXTRV Project management (04-22, 1)

- 01QAAAA Public speaking (04-22, 1)

**Electrical, Electronics and**

#### **Communications Engineering**